Showcases

事例

概要

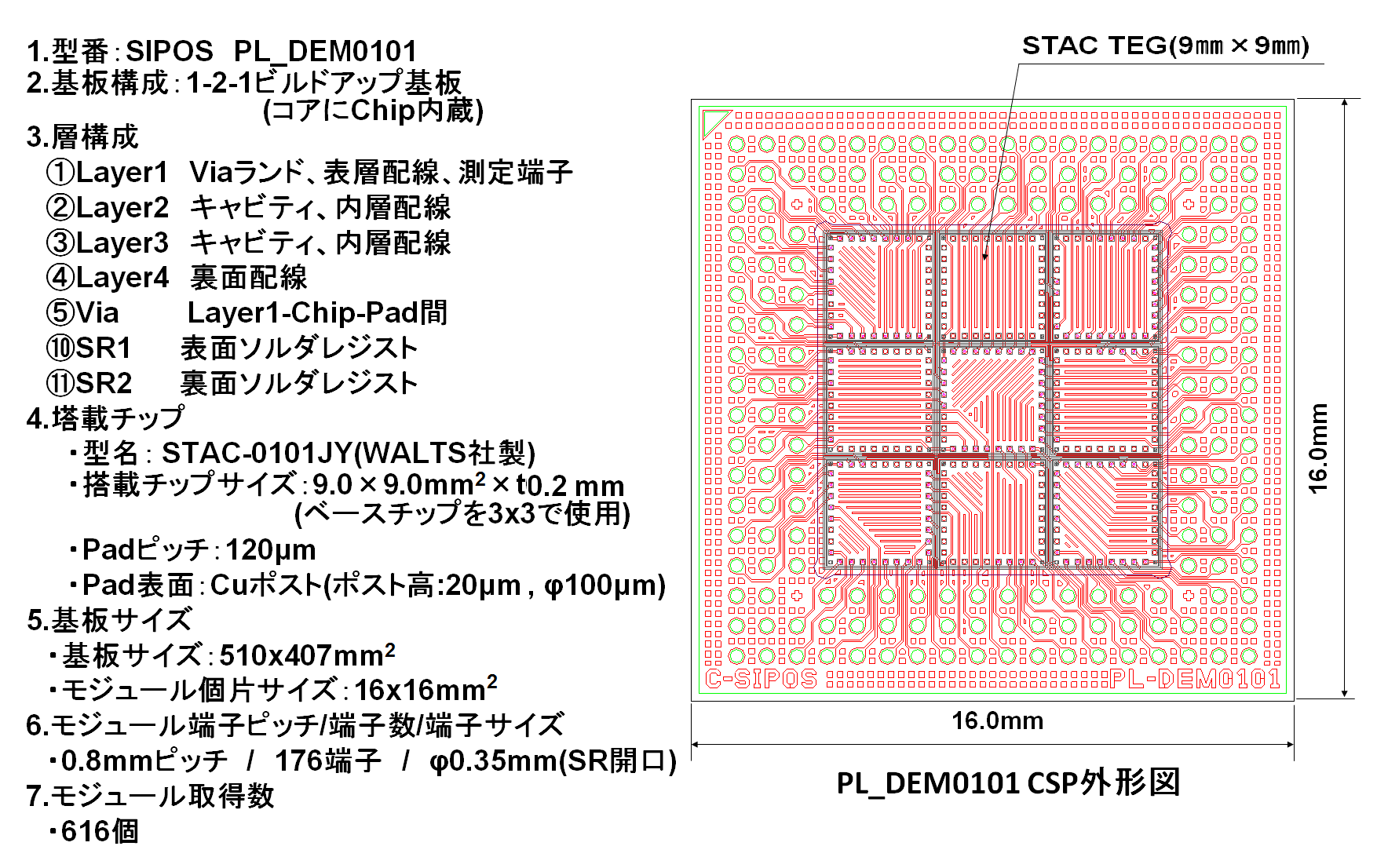

狭ピッチ、多ピンのFun-out CSPを基板サイズレベルで製造するパッケージング技術が注目を集めている。

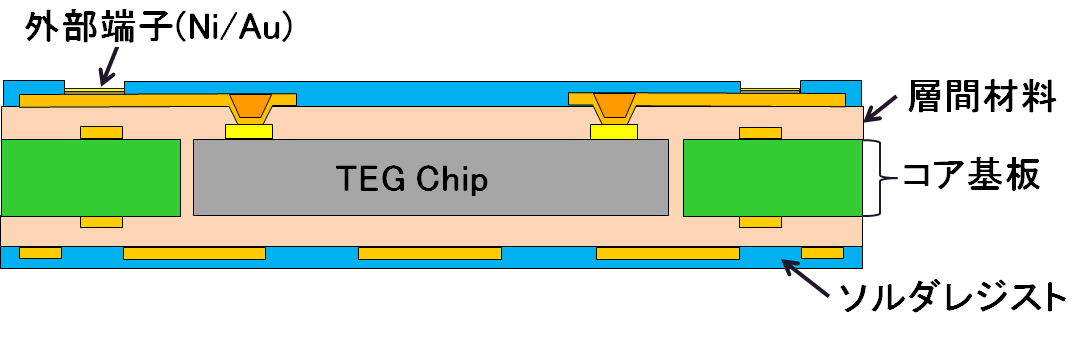

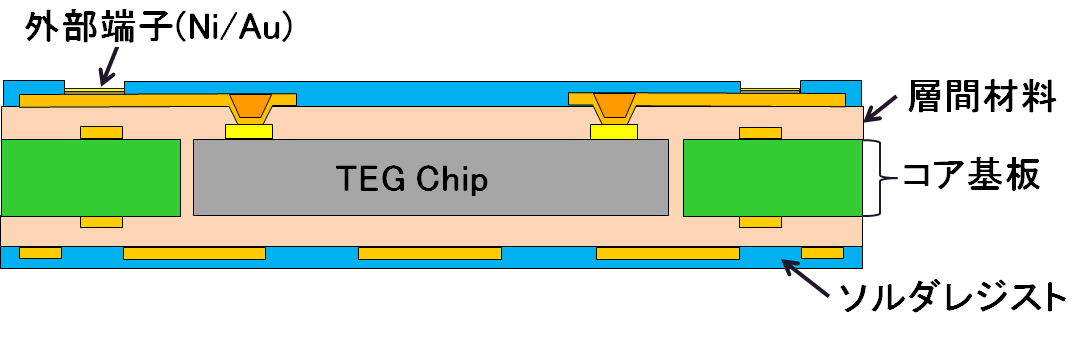

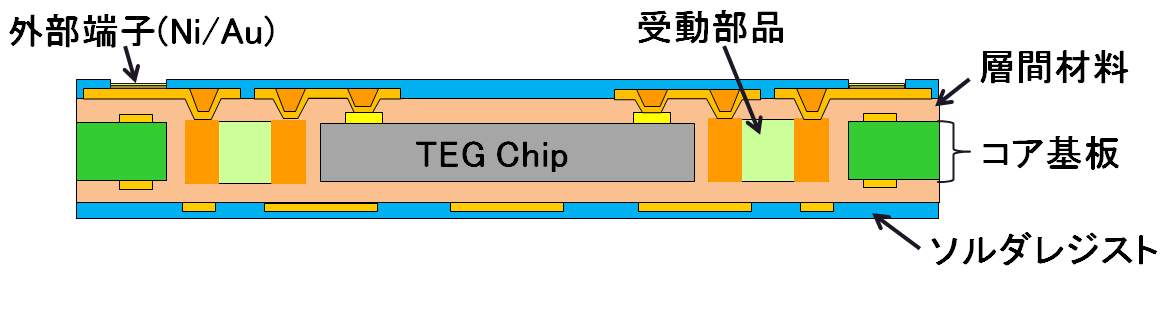

三次元半導体研究センターでは、部品内蔵技術を用いて、コア基板のキャビティ内にICチップ、受動部品を 内蔵する基板レベル部品内蔵モジュール(Panel Level _ Device Embedded Module)の構造設計、プロセス 開発を行っている。

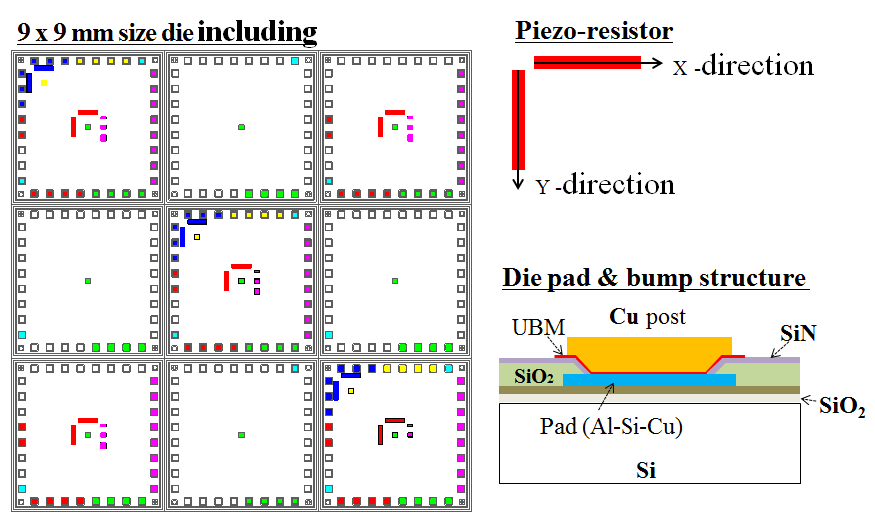

パッケージ基本仕様

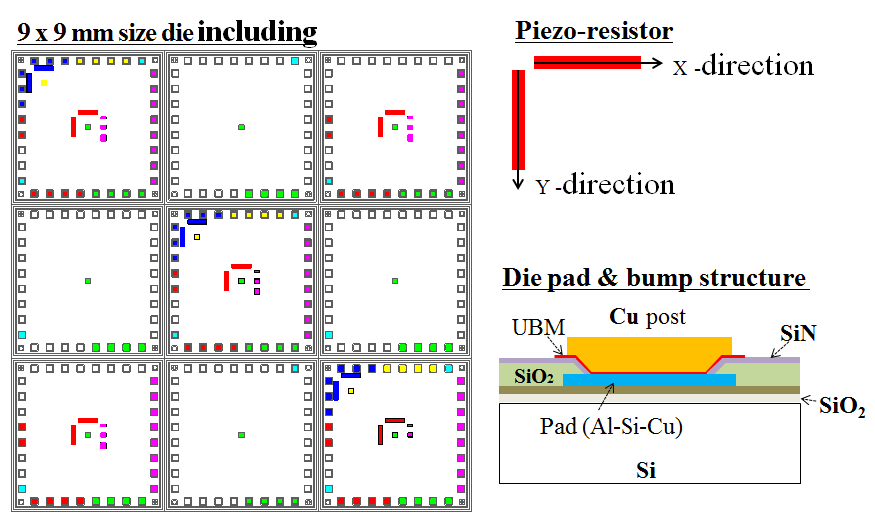

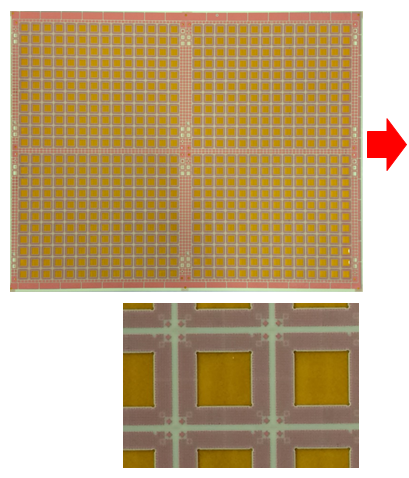

内蔵した応力評価チップ(STAC-TEG)

提供:株式会社ウォルツ社

提供:株式会社ウォルツ社

PL_DEM0101断面概略図

上記以外にもレイアウト、チップサイズ(1mm~10mm)等をカスタムで変更可能です

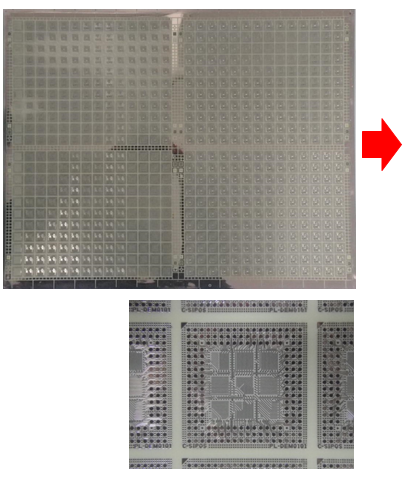

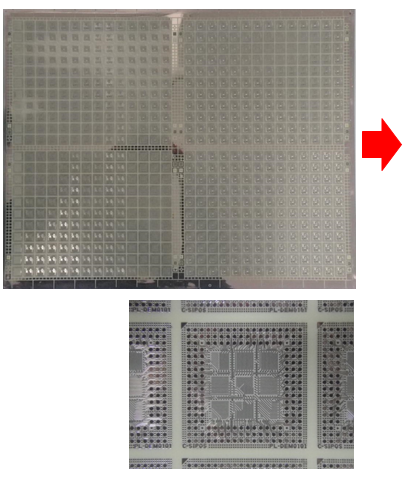

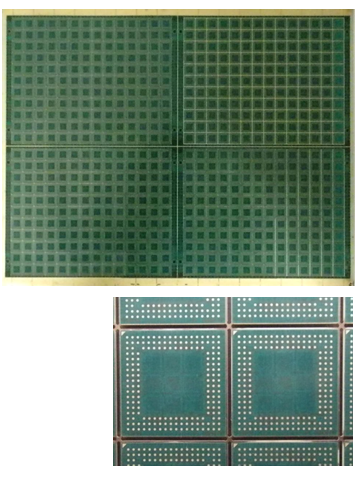

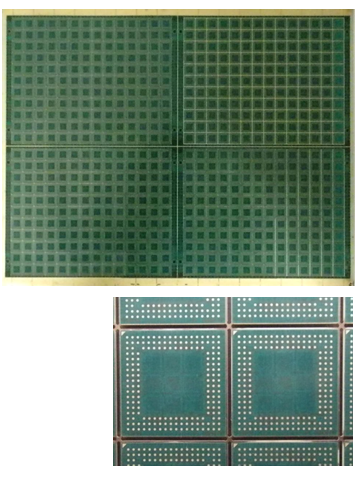

プロセス

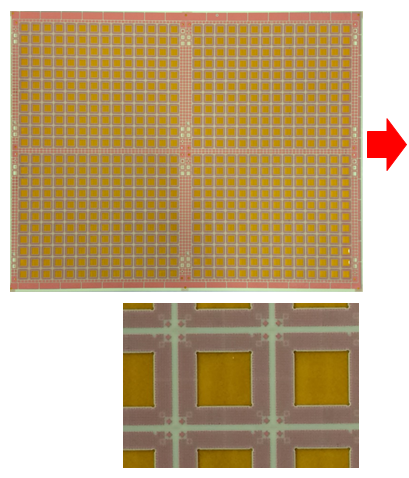

コア基板パターンニング

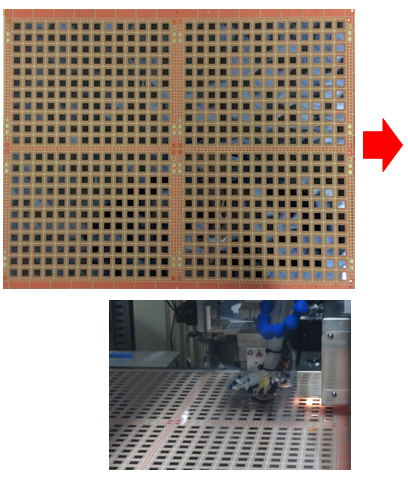

キャピティ加工

キャピティ加工

TEG-Chip搭載

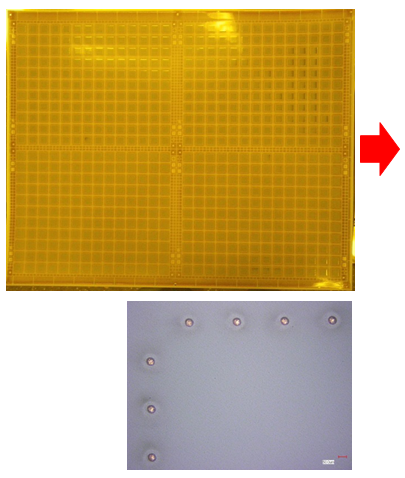

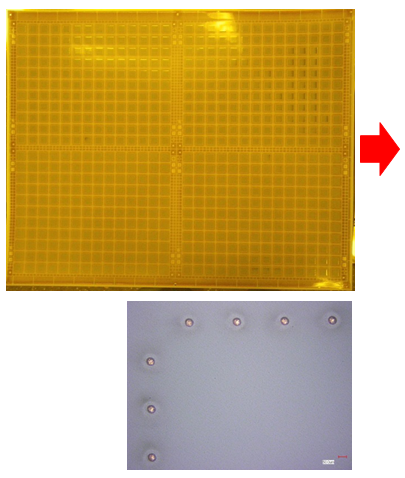

ビルドアップ材ラミネート

レーザーVia加工

レーザーVia加工

配線パターン形成

ソルダレジスト加工表面Ni/Auめっき

今後の展開

キャビティ内のICチップ周辺に受動部品を内蔵した、PL_DEM0102の作製を検討中

PL_DEM0102断面概略図