Technology Database

技術データベース

フリップチップ実装の内部応力評価

概要

三次元パッケージに適用される薄いLSIのフリップチップ実装など、PKGの薄型化により、PKG内部応力が信頼性、LSI特性に与える影響が懸念されている。

三次元半導体研究センター及び福岡大学・半導体実装研究所では、様々な材料を用いた評価基板の作製、LSIの実装、TEGチップを用いたPKG内部応力の評価をトータルで行なっている。

TEGを用いた応力評価例

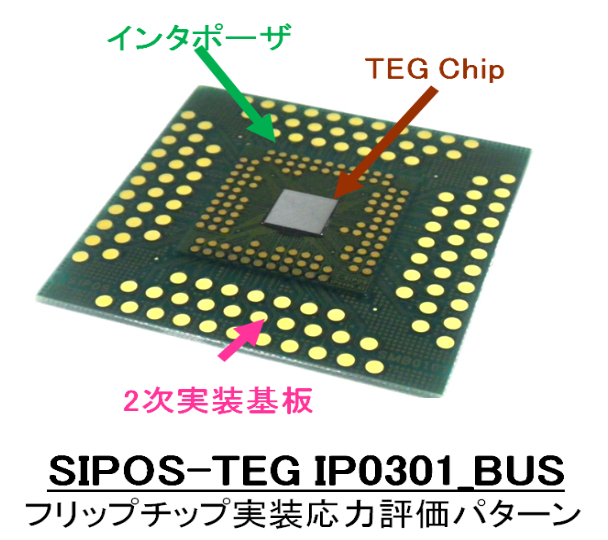

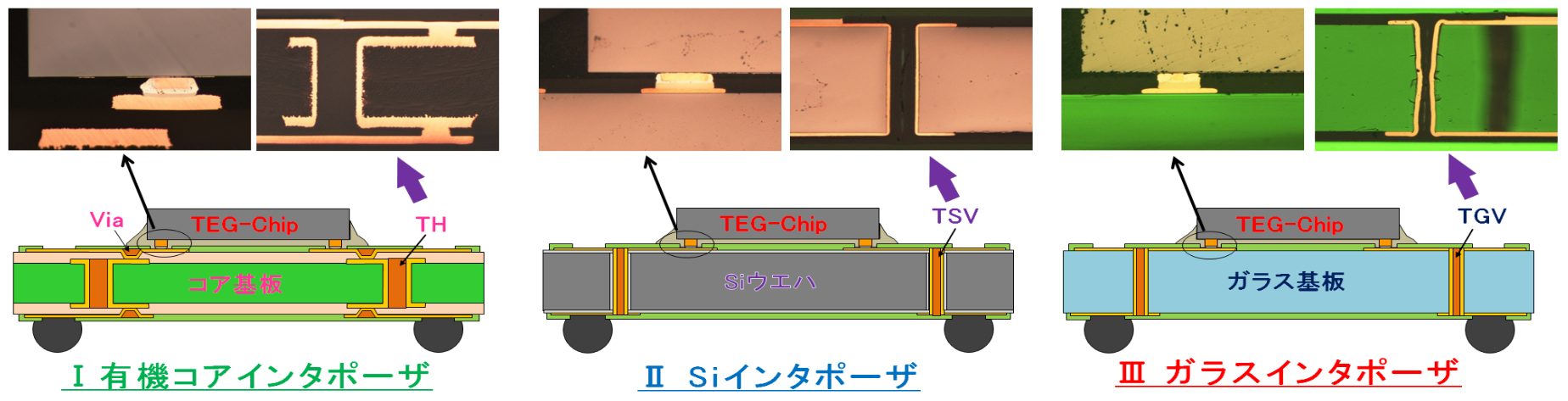

フリップチップ応力評価インタポーザ

(有機コアバージョン)

- 基板構成: 1-2-1ビルドアップ基板

- 基板サイズ:30mm×30mm×t0.37mm

- 層構成

・Layer1:ABF表面配線(Chip搭載面、測定端子)

・Layer2:コア上面配線(THランド、Viaランド)

・Layer3:コア下面配線(THランド、Viaランド)

・Layer4:ABF裏面配線(測定端子)

・SR1, SR2表裏ソルダーレジストパターン

・TH:コア基板スルーホール

・Via1 :Layer1レーザーVia

・Via2: Layer4レーザーVia - 端子表面処理:無電解Ni/Auめっき

- FC接続Padサイズ:Φ170um(SR開ロΦ120um)

- 測定端子サイズ:Φ1.5mm(SR開口Φ1.2mm)

- 測定端子数:108端子

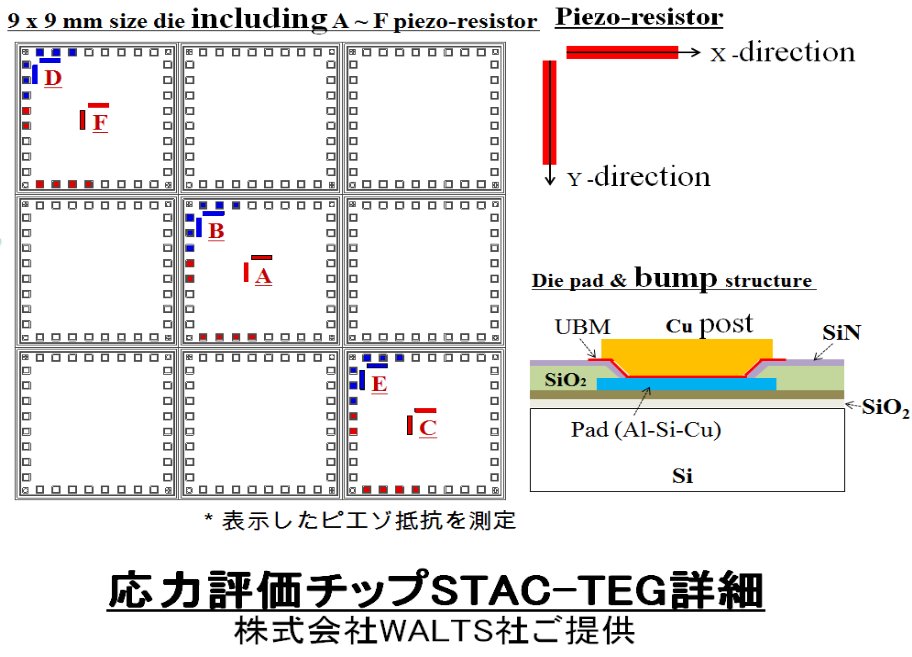

- 搭載Chip:STAC-TEG 3×3 (9.0mm角)

評価構造例

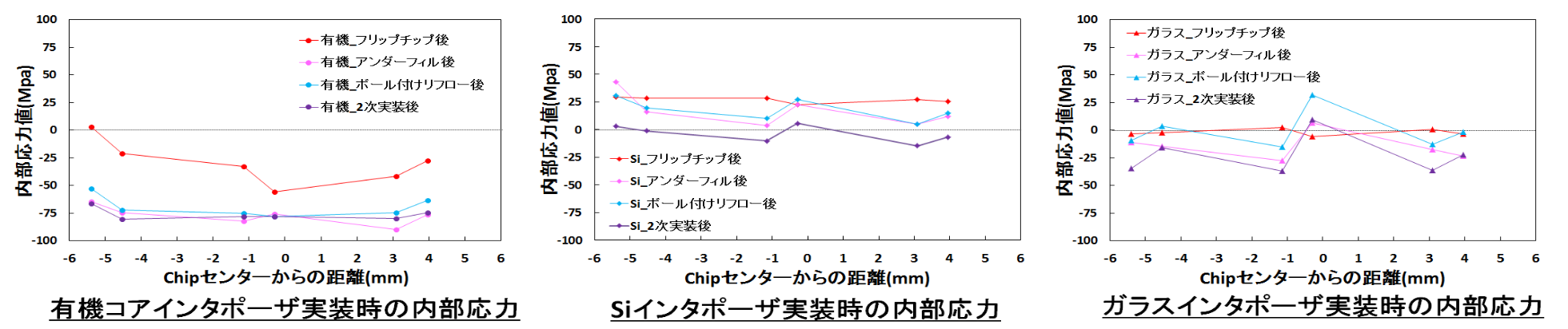

応力測定結果例

インタポーザ構成材料により内部応力に大きな差があることが判る